## Integrating 2D Ferroelectric $CuInP_2S_6$ with $MoS_2$ Field Effect Transistor

### Abstract

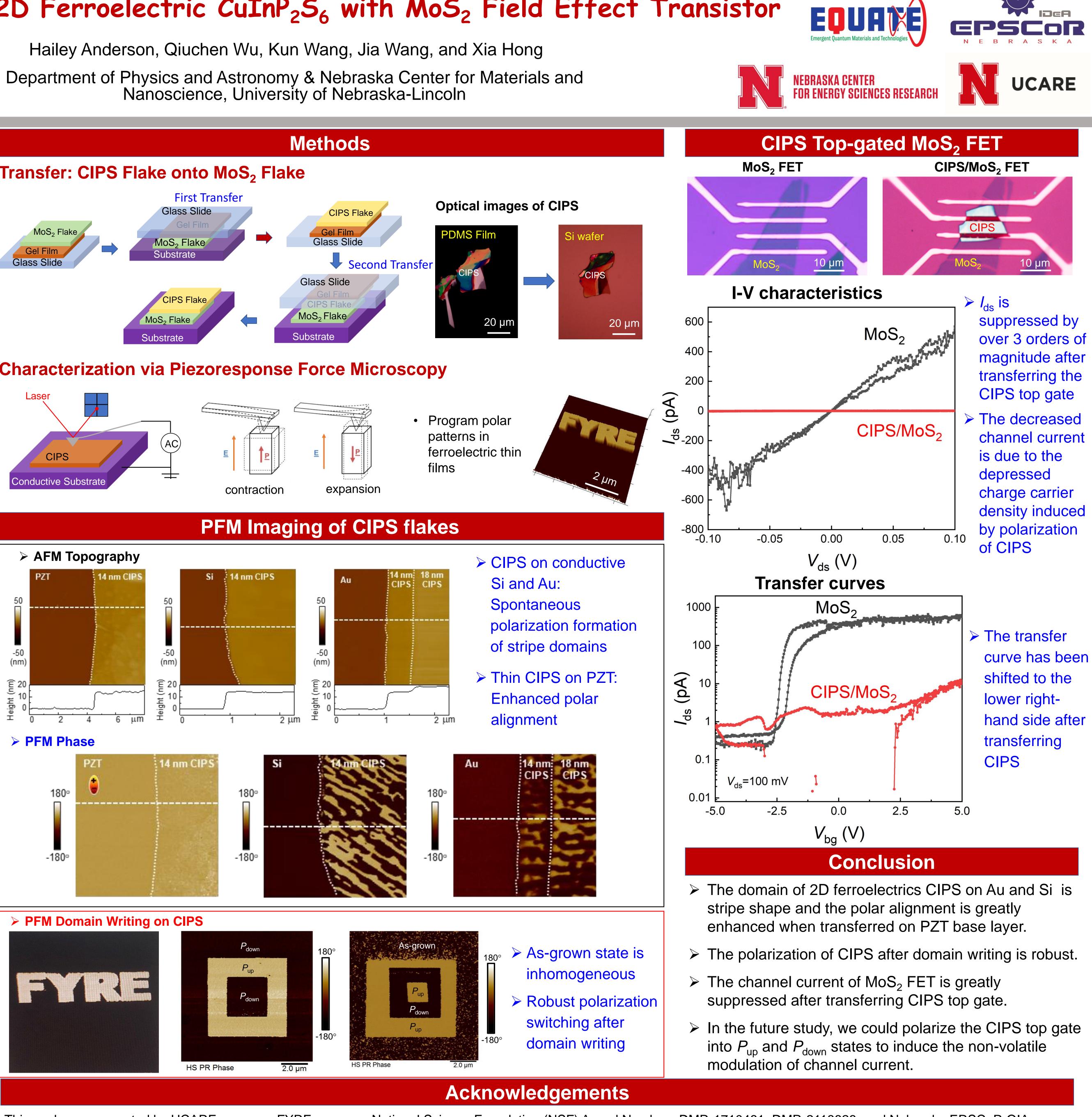

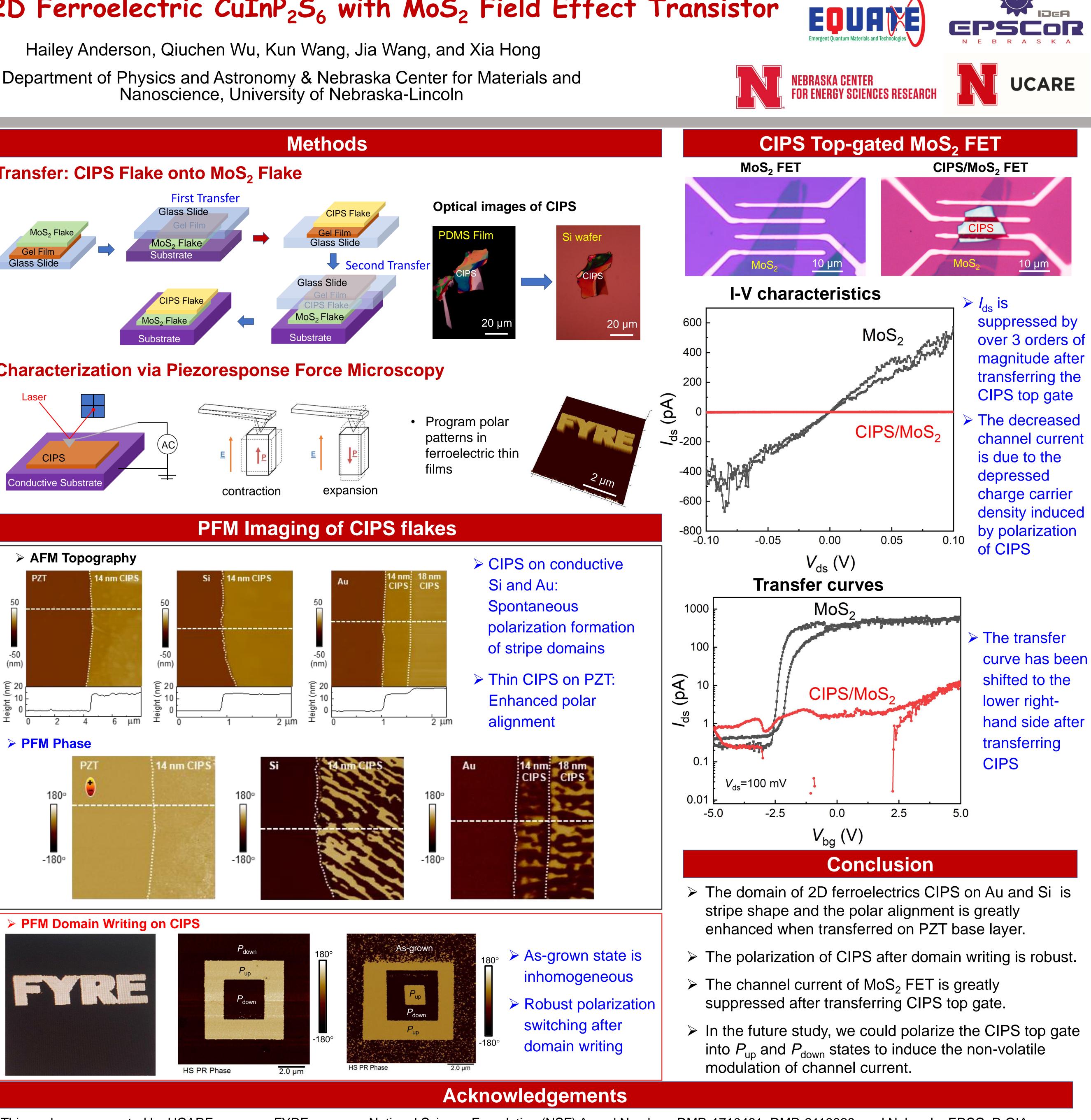

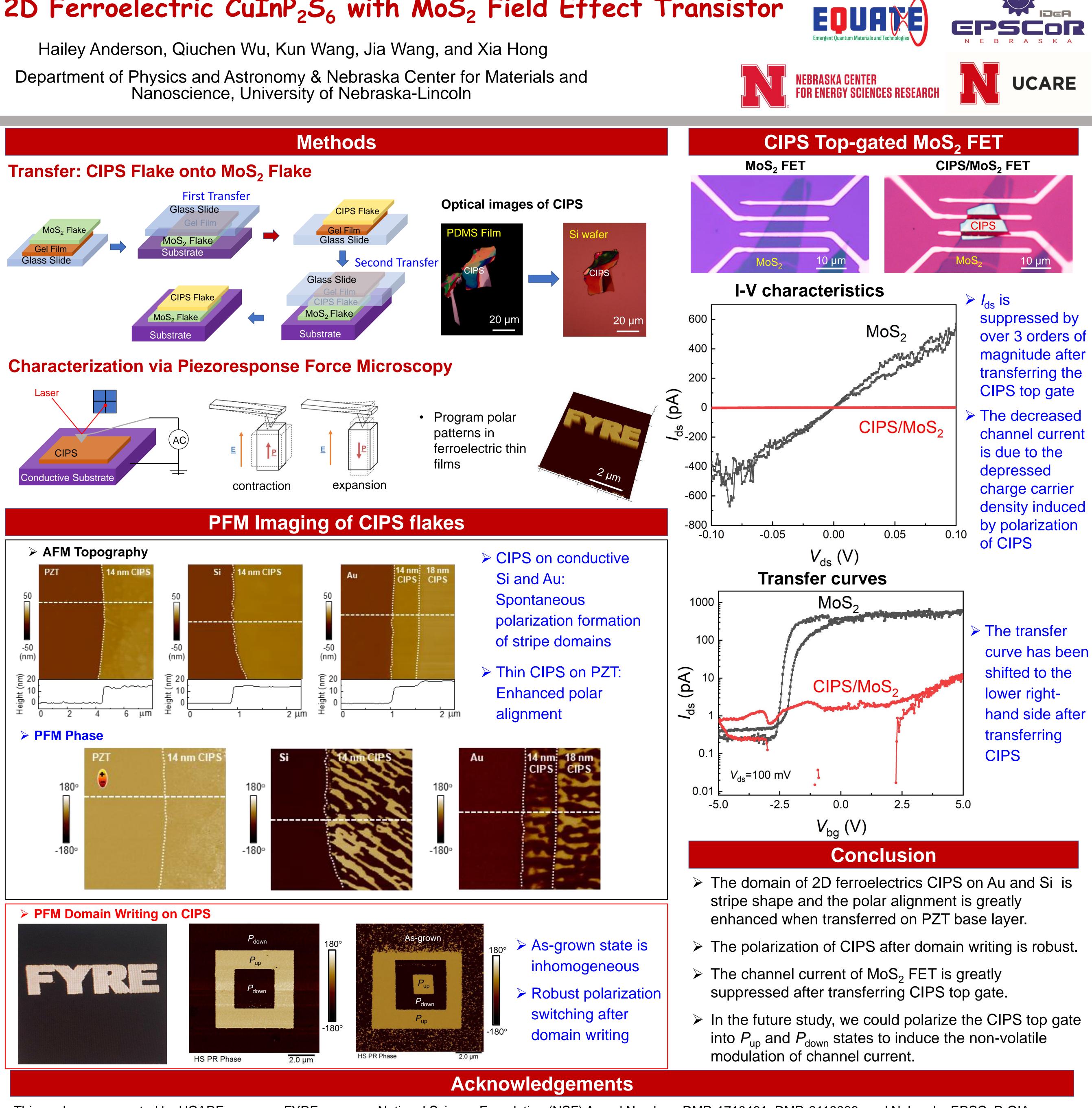

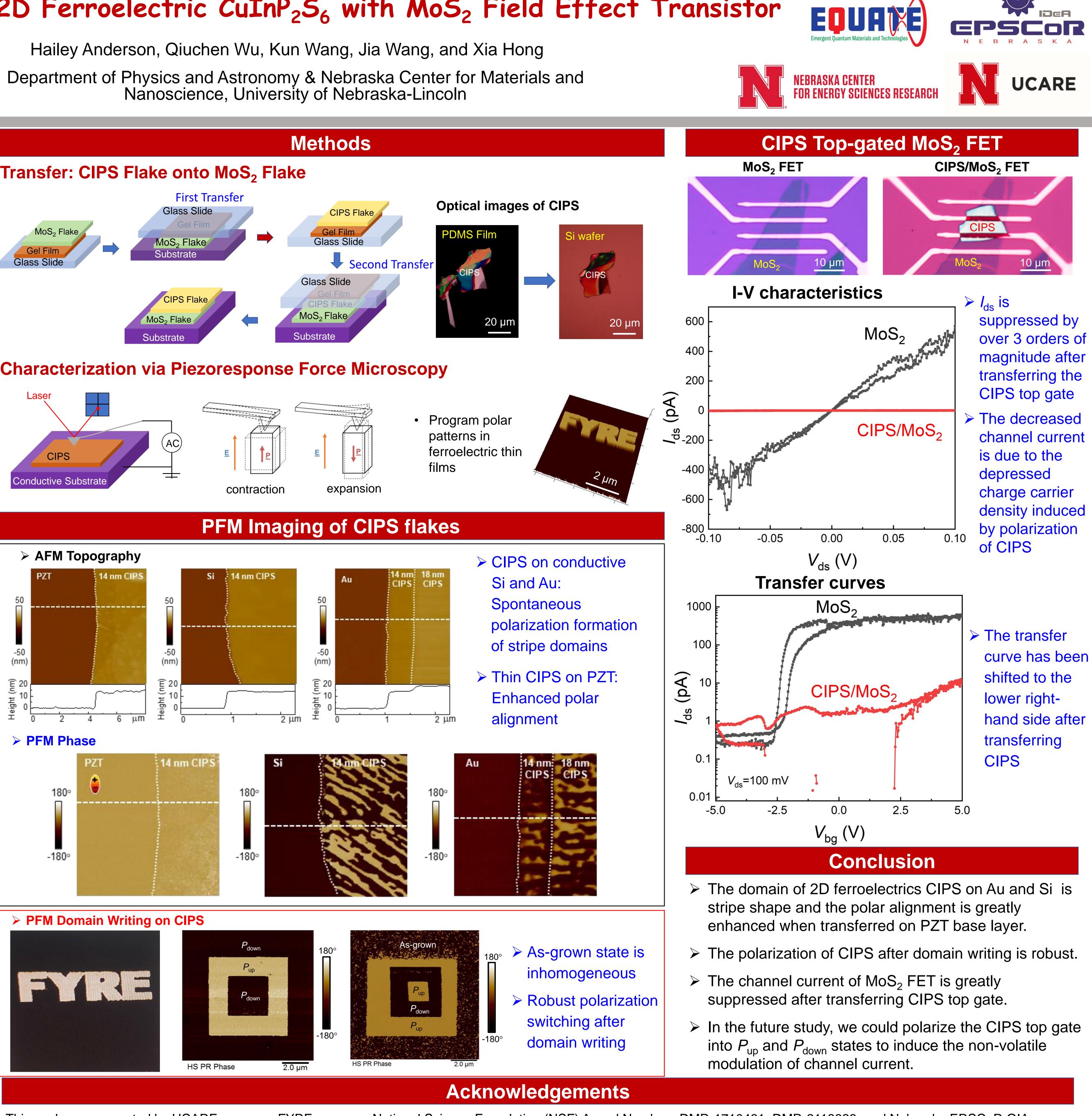

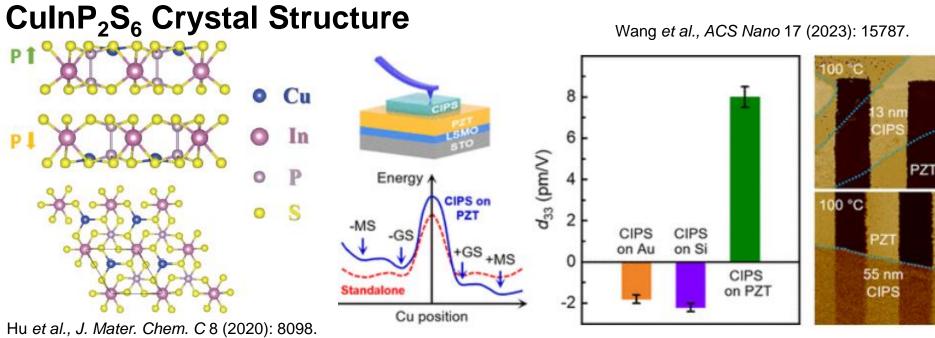

This study examined the gating effect of two dimensional (2D) van der Waals (vdW) ferroelectrics CuInP<sub>2</sub>S<sub>6</sub> (CIPS) in modulation of channel current of 2D semiconductor MoS<sub>2</sub> field effect transistor (FET). Recently, ferroelectricity has been discovered in 2D vdW materials, such as SnTe, In<sub>2</sub>Se<sub>3</sub>, and CIPS. These materials can potentially preserve ferroelectricity in the monoatomic layer limit, making them promising for developing ferroelectric-based 2D nanoelectronics.

In this study, we explored the gating effect on 2D MoS<sub>2</sub> FET top gated by 2D vdW ferroelectrics CIPS. The polarizations of CIPS on different base layers are robust after domain writing using conductive atomic force microscopy (AFM). The channel conductance has been sufficiently suppressed after transferring the CIPS top gate on MoS<sub>2</sub>, which is due to the charge carrier depletion induced by the polarization of as-grown CIPS. In the future study, we could use piezoresponse force microscopy (PFM) to switch the polarization of the CIPS top gate into the  $P_{up}$  and  $P_{down}$  states, which might induce non-volatile modulation of channel current and achieve the different current on/off ratios. Our research can provide important material parameters for designing CIPSbased nanoelectronic devices, paving the path for their implementation in programmable, flexible nonvolatile memory, neuromorphic computing, and optoelectronic applications.

Introduction

# **∽**DW • Ferroelectric shows the piezoelectric response under external

electric fields • Non-volatile polarization and switchable hysteresis

### **2D** van der Waals (vdW) Ferroelectrics

• 2D vdW ferroelectrics can preserve ferroelectricity in the atomic layer limit, which is compromised for conventional ferroelectrics

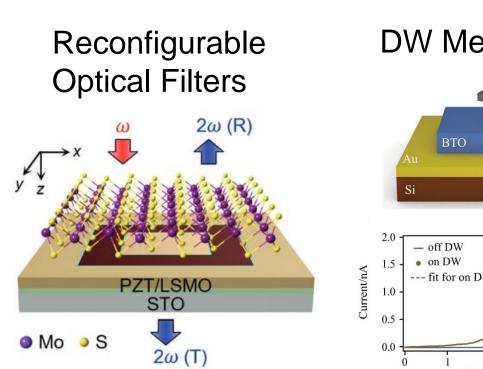

### Application

**Ferroelectrics**

Wu et al., ACS Nanosci. Au 3 (2023): 482

Li et al., Adv. Mater. 35 (2023): 2208825

**DW Memories** -- fit for on DW 1 2 3 4 Voltage/V 4

Sun et al., Nat Commun 13 (2022): 4332.

2044049, and Nebraska Center for Energy Sciences Research (NCESR).